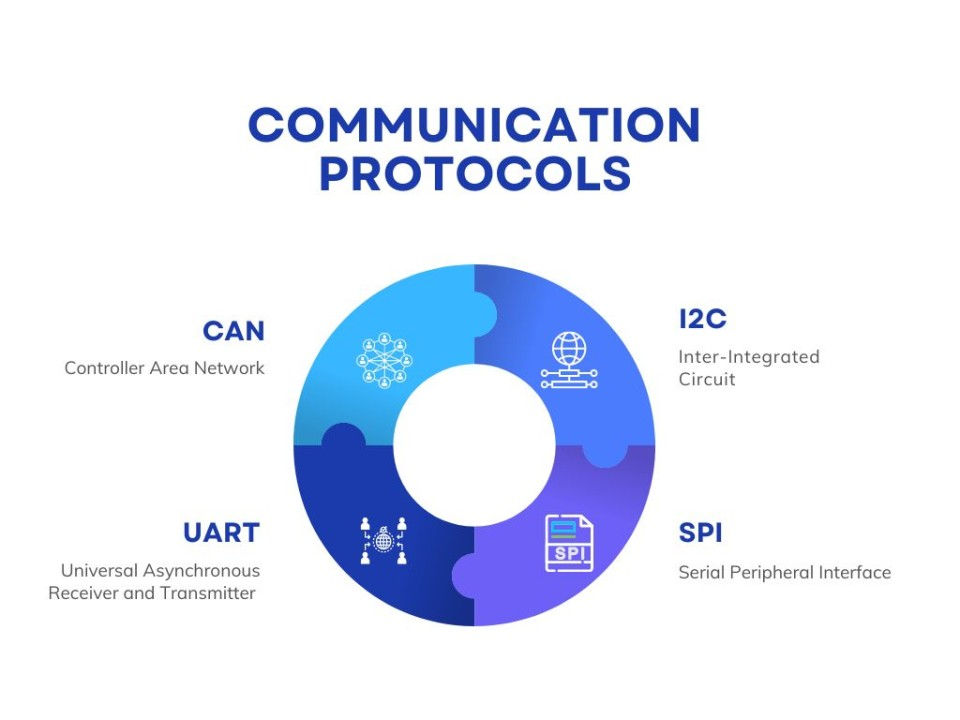

嵌入式通讯协议

UART

- RX 接收

- TX 发送

I2C

信号线

- SDA 数据

- SCL 时钟

SPI

引脚

| 引脚名称 | 功能描述 | 主设备 (Master) | 从设备 (Slave) |

|---|---|---|---|

| SCLK | 串行时钟(Serial Clock):由主设备生成的时钟信号,用于同步数据传输。 | 输出 | 输入 |

| MOSI | 主输出从输入(Master Out Slave In):主设备向从设备发送数据的信号线。 | 输出 | 输入 |

| MISO | 主输入从输出(Master In Slave Out):从设备向主设备发送数据的信号线。 | 输入 | 输出 |

| CS/SS | 片选(Chip Select)/从属选择(Slave Select):用于选择从设备的信号,通常为低电平有效。 | 输出 | 输入 |

调试协议

JTAG

信号线

- TMS(Test Mode Select) 模式选择信号,引导 TAP 进入不同的状态,如 Shift-DR、Shift-IR、Capture 或 Update 等状态

- TCK(Test Clock) 时钟信号

- TDI(Test Data In) 数据流向:调试器 → 被调试设备(Target)

- TDO(Test Data Out) 数据流向:被调试设备(Target) → 调试器。

SWD

调试STM32设备协议,由JTAG转化而来的升级版;

信号线

- SWDIO:双向数据传输线,用于发送和接收数据。

- SWCLK:时钟信号。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 铸鼎-BuildDing!

评论